AMD Shows Off Original Ryzen 9 5950X3D V-Cache Prototype

16 cores with two V-Cache chiplets were tested, but not realistic for the mainstream market

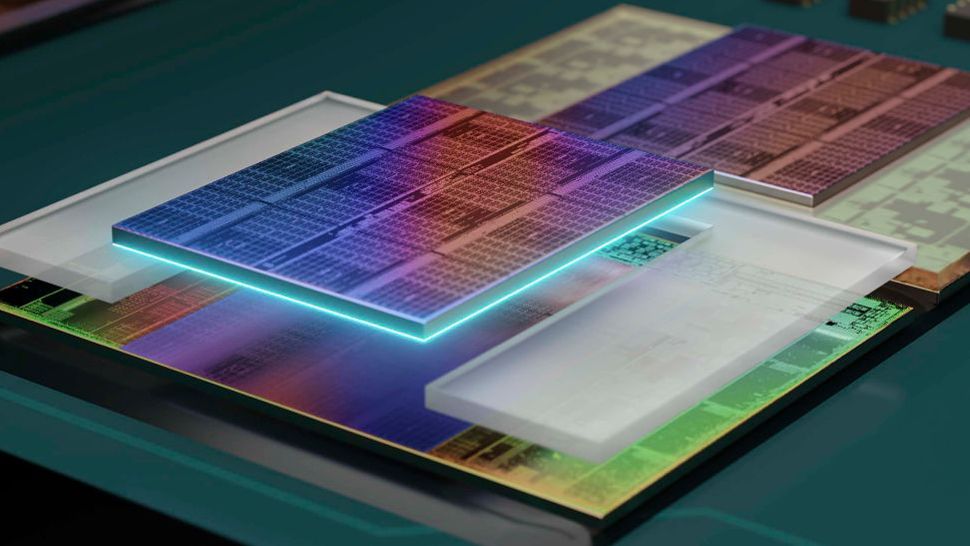

In an interview with Gamers Nexus, AMD’s Amit Mehra and Bill Alverson shared the origin story of AMD’s 3D-VCache technology and how the technology became present on its mainstream Ryzen consumer desktop platform — including some of the Best CPUs for Gaming. During their discussion with Gamer Nexus’ Steve Burke, the duo showed off prototypes of AMD’s first Ryzen 3D-VCache parts, including 12-core and 16-core models with dual CCD 3D-VCache designs.

AMD’s insight highlights the fact that the company was actually looking into producing high-core count Ryzen 5000 products with 3D-VCache technology as many enthusiasts have theorized. It also confirms that AMD was not architecturally limited to building an 8-core design alone, but had the physical production capability to produce multi-CCD 12-core and 16-core Ryzen 5000X3D chips if it wanted to.

According to AMD’s Amit Mehra, the desktop implementation of AMD’s 3D-VCache technology started as an accident. The original implementation was designed for servers only, with AMD originally only testing 3D-VCache iterations of its EPYC server CPUs.

The reason AMD opted to research 3D-Vcache functionality on Ryzen in the first place, was due to an “accident” during the production of presumably prototype Epyc 3D-VCache chips where 7 CCDs were left over in a batch that couldn’t be utilized in an EPYC chip — since EPYC CPUs required 8 CCDs at the time.

This led Mehra and his cohorts to re-purpose the seven V-Cache-equipped dies for desktop use, building out multiple designs including 8, 12, and 16 core variants. This is what lead AMD to research the capabilities of 3D-VCache in desktop workloads and discover the incredible gaming performance V-Cache offers, giving birth to the Ryzen 7 5800X3D.

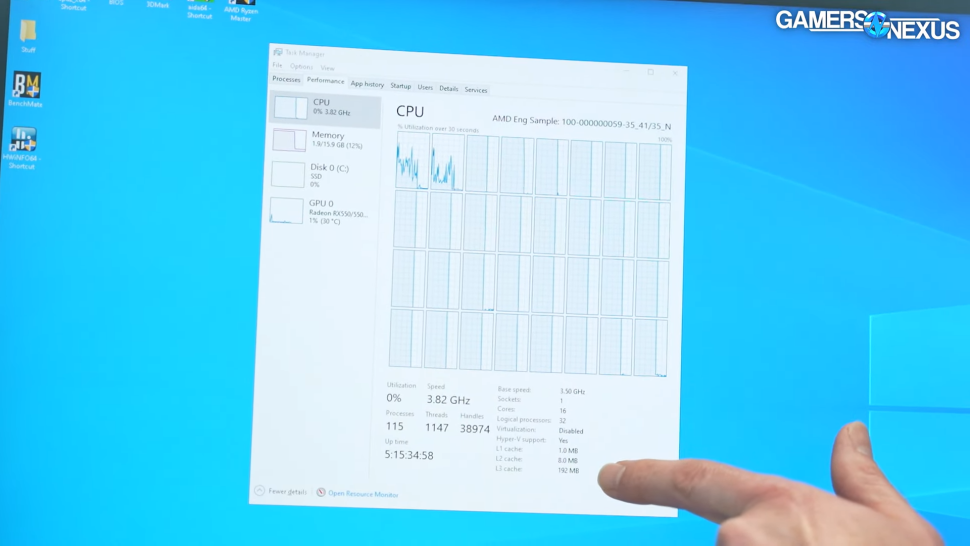

AMD showed off two functional high-core counts Zen 3 X3D prototypes to Gamers Nexus, including a 16-core and 12-core model featuring 3D-VCache on both CCDs. The chips were fully functional within Windows actively and were shown actively running an AIDA64 stress test on screen. Bill Alverson showed a glimpse of the chip’s specs in Task Manger, revealing the massive 192MB of L3 cache equipped on both CPUs, thanks to the “dual 3D-VCache” implementation.

Alverson and Mehra didn’t disclose AMD’s exact reasons for not shipping out 12-core and 16-core Ryzen 5000X3D CPUs, however, they did highlight the disadvantages of 3D-VCache on Ryzen CPUs with two CCD, since there is a large latency penalty that occurs when two CCDs talk to each other through the Infinity Fabric, nullifying any potential benefits the 3D-VCache might have when an application is utilizing both CCDs.

Obviously, at the time AMD didn’t take into account hybrid users that might want a high core count X3D chip for work and play, but it is something they were thinking about and something it rectified with the release of its Ryzen 9 7950X3D and 7900X3D.

© 2025 Zeon Technology